सामग्री

- व्याख्या - फेज-लॉक लूप (पीएलएल) म्हणजे काय?

- मायक्रोसॉफ्ट अझर आणि मायक्रोसॉफ्ट क्लाऊडची ओळख | या संपूर्ण मार्गदर्शकामध्ये आपण क्लाउड संगणन करणे म्हणजे काय आणि मायक्रोसॉफ्ट अझर आपल्याला क्लाऊडवरून आपला व्यवसाय स्थलांतरित आणि चालविण्यात कशी मदत करू शकेल हे शिकाल.

- टेकोपीडिया फेज-लॉक केलेल्या लूप (पीएलएल) चे स्पष्टीकरण देते

व्याख्या - फेज-लॉक लूप (पीएलएल) म्हणजे काय?

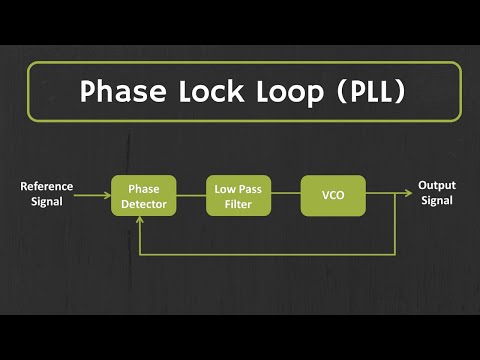

फेज-लॉक लूप (पीएलएल) इलेक्ट्रॉनिक सर्किटरीचा एक प्रकार आहे ज्यामध्ये व्होल्टेज / वर्तमान चालित ऑसीलेटर असतो जो फेज डिटेक्टरसह जोडला जातो आणि त्याचे इनपुट आणि आउटपुट एकमेकांशी सतत टप्प्यात ठेवतो. फेज डिटेक्टरचे कार्य हे ऑसीलेटरच्या नियतकालिक सिग्नलच्या अवस्थेस इनपुट सिग्नलशी जुळविणे आणि थर थर थोड्या थोड्या अंतरावर गेल्यास थरथरणा .्या यंत्रणा दुरुस्त करणे होय. इनपुटला आउटपुट परत दिले म्हणून याला फीडबॅक लूप असे म्हणतात.

मायक्रोसॉफ्ट अझर आणि मायक्रोसॉफ्ट क्लाऊडची ओळख | या संपूर्ण मार्गदर्शकामध्ये आपण क्लाउड संगणन करणे म्हणजे काय आणि मायक्रोसॉफ्ट अझर आपल्याला क्लाऊडवरून आपला व्यवसाय स्थलांतरित आणि चालविण्यात कशी मदत करू शकेल हे शिकाल.

टेकोपीडिया फेज-लॉक केलेल्या लूप (पीएलएल) चे स्पष्टीकरण देते

फेज-लॉक लूप निश्चित करतो की रिअल टाइममध्ये टेलिकम्युनिकेशन सिग्नल एका विशिष्ट वारंवारतेवर लॉक केलेला असतो, नसल्यास तो सतत तुलना आणि अभिप्राय देऊन वारंवारता दुरुस्त करण्याचा प्रयत्न करतो. पीएलएल हे टेलिकम्युनिकेशन चॅनेलमध्ये स्टेबलायझर्स, मॉड्यूलेटर, डिमोड्युलेटर, आवाज काढणारे आणि फ्रीक्वेन्सी डिव्हिडर्स म्हणून आढळतात. ते वायरलेस संप्रेषणात वापरले जातात, विशेषत: मोठेपणा मॉड्यूलेशन (एएम), फ्रिक्वेन्सी मॉड्युलेशन (एफएम) तसेच फेज मॉड्यूलेशन (पीएम) मध्ये. डिजिटल संप्रेषण हाताळू शकणारे इंटिग्रेटेड सर्किट (आयसी) च्या स्वरूपात बहुतेक सामान्यपणे डिझाइन केलेले, पीएलएल हे डिजिटल आणि अॅनालॉग दोन्ही संप्रेषणासाठी सर्वात महत्वाचे घटक आहेत. फेज-लॉक लूप वारंवारता नियंत्रण वापरणारे वायरलेस कम्युनिकेशन-एडिंग उपकरणे देखील वारंवारता-संश्लेषित असे म्हणतात.